TAMPERE, Finlândia 14/12/2021 –

O primeiro ‘System on Chip’ (SoC) desenvolvido pelo consórcio Finnish SoC Hub foi lançado. As parcerias do projeto se concentrarão a seguir na melhoria do design, automação e desempenho do SoC. O primeiro dos três chips a serem desenvolvidos pelo consórcio estará pronto para implantação no início de 2022. O projeto contribui para reforçar a soberania tecnológica da Europa.

Este comunicado de imprensa inclui multimédia. Veja o comunicado completo aqui: https://www.businesswire.com/news/home/20211213005533/pt/

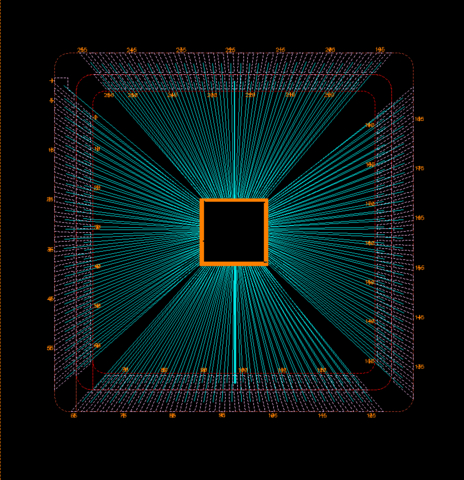

The bonding diagram image shows how the chip IO pads are wired to the package pins. The package is soldered to the printed circuit board. The layout picture depicts how the functional blocks are physically located on the chip. The IO pads that are bonded to the package pins are shown on the sides. Photos: SoC Hub. (Graphic: Business Wire)

O SoC Hub finlandês tem como objetivo desenvolver o domínio do design de SoC como pioneiro na Europa e aprimorar a posição competitiva da Finlândia. A iniciativa do SoC Hub, coordenada pela Universidade de Tampere da Finlândia e da Nokia, foi lançada no ano passado. As atividades de cocriação realizadas pelas parcerias vão muito além do escopo de um projeto de pesquisa convencional.

“O SoC foi desenvolvido com o uso dos mesmos métodos que são utilizados na produção industrial, como design para capacidade de teste, verificação extensiva e foco na integração de níveis de sistemas em vez de módulos únicos”, disse Ari Kulmala, professor de Prática em Design de SoC na Universidade de Tampere.

Segundo Kulmala, o chip também pode ser testado por partes interessadas externas, já que inclui um kit de desenvolvimento, e pode ser integrado em uma vários outros sistemas.

Uma das principais metas do projeto do SoC Hub é possibilitar a prototipagem rápida para novas ideias, por exemplo, na Internet das Coisas (IoT), aprendizagem automática e tecnologias 5G e 6G em silício.

O chip Ballast recém-lançado é o primeiro de uma série de três chips. O chip será fabricado pela TSMC, a maior fabricante mundial de chips semicondutores.

O chip é fabricado com uso do recente processo de dispersão ultrabaixa de 22 nm da TSMC, que é especialmente adequado para dispositivos IoT e Edge. O reator contém vários núcleos de CPU RISC-V diferentes, um processador de sinal digital, um acelerador de IA, interfaces ricas do tipo sensor e uma interface de extensão para FPGA. Um conjunto completo de software – incluindo drivers, ferramentas de desenvolvimento de software e suporte para depuração de chip – também foi implementado. O chip é compatível com sistemas operacionais em tempo real e o Linux ao mesmo tempo.

“Foi um prazer trabalhar com a equipe do SoC Hub. Eles desenvolveram o chip com extrema rapidez e a qualidade do trabalho foi excelente”, declarou Bas Dorren, diretor de Desenvolvimento de Negócios no imec.IC-link, parte do imec (um centro de P&D para tecnologias nano e digital).

Outros dois chips serão lançados nos próximos dois anos

Devido a seu grande tamanho, o chip foi criado em muito pouco tempo. O ambicioso objetivo foi alcançado graças ao bom espírito de equipe eàcompetência e experiência dos especialistas envolvidos.

“Muito trabalho foi feito para permitir uma cooperação perfeita entre a Universidade e as parcerias da empresa. Diversos pesquisadores em início de carreira participaram da concepção do Ballast e assim tiveram a oportunidade de aplicar os conhecimentos adquiridos em seus estudos em um projeto industrial”, disse Timo Hämäläinen, chefe da Unidade de Ciências da Computação da Universidade de Tampere.

Além do desenvolvimento do SoC, a primeira fase do projeto também foi uma grande empreitada, que envolveu a criação do consórcio e a preparação do software, além dos contratos de licença necessários. Liderado pela Universidade de Tampere e a Nokia, o consórcio é formado por CoreHW, VLSI Solution, Siru Innovations, TTTEch Flexibilis, Procemex, Wapice e Cargotec como parcerias.

No projeto financiado pela Business Finland, três SoCs serão lançados até o final de 2023. Casos de uso para os chips serão planejados em conjunto com o consórcio do projeto.

“Nas próximas fases do projeto, vamos nos concentrar ainda mais na sistemática, automação e desempenho dos SoCs. Apesar de termos atingido nossa primeira meta, vamos continuar avançando sem demora. A hora de investir no desenvolvimento de SoC é agora, não amanhã”, enfatizou Timo Hämäläinen.

Universidade de Tampere

A multidisciplinar Universidade de Tampere é a segunda maior universidade da Finlândia. As liderançasàfrente de nossa pesquisa e aprendizagem são a tecnologia, a saúde e a sociedade. A Universidade está empenhada em enfrentar os maiores desafios que nossa sociedade enfrenta e criar novas oportunidades. Quase todas as áreas de estudo internacionalmente reconhecidas estão representadas na Universidade. Juntas, a Universidade de Tampere e a Universidade de Ciências Aplicadas de Tampere compreendem a comunidade das Universidades de Tampere composta por mais de 30.000 alunos e cerca de 5.000 funcionários.www.tuni.fi/en

O texto no idioma original deste anúncio é a versão oficial autorizada. As traduções são fornecidas apenas como uma facilidade e devem se referir ao texto no idioma original, que é a única versão do texto que tem efeito legal.

Ver a versão original em businesswire.com: https://www.businesswire.com/news/home/20211213005533/pt/

Contato:

Perguntas:

Timo Hämäläinen

Chefe da Unidade de Ciências da Computação da Universidade de Tampere

Ari Kulmala

Professor de Prática em Design ‘System on Chip’ na Universidade de Tampere

Fonte: BUSINESS WIRE